J. Lin and B. Haroun, "An embedded 0.8 V/480 μW 6B/22 MHz flash ADC in 0.13 μm digital CMOS Process using a nonlinear double interpolation technique," IEEE JSSC, vol. 37, pp. …

CMOS Comparators Basic Concepts Need to provide high gain, but it doesn’t have to be linear ¾ Don’t need negative feedback and hence don’t have to worry about phase margin. ¾ The gain …

Evaluate VOH, VOL, Av(0), Vin(min), p1, p2, for the two-stage comparator shown in Fig. 8.2-1. Assume that this comparator is the circuit of Ex. 6.3-1 with no compensation capacitor, Cc, …

An Overview Of Dynamic CMOS Comparators - IEEE Xplore

This paper reviewed the performance of some popular dynamic CMOS comparators such as strong arm latch comparator, dynamic latched comparator, resistive diode comparator, double …

CMOS Comparators Course Integrated Circuit Design, 2009 Franco Maloberti Department of Electronics University of Pavia Franco Maloberti – CMOS Comparators, 2009 1/43. Outline 1 …

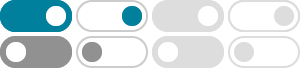

Regenerative comparators use positive feedback to accomplish the comparison of two signals. Latches can have a faster switching speed than the previous comparators. NMOS and PMOS …

What is a Comparator? The comparator is a circuit that compares one analog signal with another analog signal or a reference voltage and outputs a binary signal based on the comparison. …

Lecture 33 – High Speed Comparators (6/26/14) Page 33-5 CMOS Analog Circuit Design © P.E. Allen - 2016 Maximizing Speed for Slew Rate Limitation The key is to make the …

single-ended auto-zeroing comparator is examined, followed by simple and mul- tistage differential comparators, regenerative comparators, and fully differential comparators.

Cmos fully dynamic latched comparators are majorly used in Analog to Digital converters (ADCs), data receivers and Memory Sense Amplifiers (SAs) because they provide high speed, reduced …